ELSEVIER

Contents lists available at ScienceDirect

#### International Journal of Thermal Sciences

journal homepage: www.elsevier.com/locate/ijts

## Transistor-level thermal management in wide and ultra-wide bandgap power semiconductor transistors: A review

Guangzheng Zhang <sup>a</sup>, Shilin Dong <sup>a,b</sup>, Qian Xin <sup>c</sup>, Lin Guo <sup>a,b</sup>, Xinyu Wang <sup>d</sup>, Gongming Xin <sup>a,e,\*</sup>, <sup>b</sup>, Ning Qin <sup>a</sup>, Xin Lan <sup>a</sup>, Chunsheng Guo <sup>f</sup>, Wei Wang <sup>g</sup>, Bing-yang Cao <sup>h,\*\*</sup>

- <sup>a</sup> School of Energy and Power Engineering, Shandong University, Jinan, 250061, China

- <sup>b</sup> Shenzhen Research Institute of Shandong University, Shenzhen, 518063, China

- <sup>c</sup> School of Integrated Circuits, Shandong University, Jinan, 250101, China

- <sup>d</sup> Institute of Thermal Science and Technology, Shandong University, Jinan, 250061, China

- Shandong Institute of Advanced Technology, Jinan, 250100, China

- f School of Mechanical, Electrical & Information Engineering, Shandong University, Weihai, 264209, China

- g School of Integrated Circuits, Peking University, Beijing, 100871, China

- h Key Laboratory for Thermal Science and Power Engineering of Ministry of Education, Department of Engineering Mechanics, Tsinghua University, Beijing, 100084, China

#### ARTICLE INFO

# Keywords: Ultra-wide bandgap Transistor-level Thermal management Self-heating Power semiconductor transistor

#### ABSTRACT

Power electronics are advancing in efficiency and power density, but high-frequency, miniaturization, and integration introduce novel thermal management challenges. Effective thermal management is crucial to maintaining the efficient operation of semiconductor transistors. As package-level thermal management approaches its heat dissipation limits, transistor-level thermal management near the junction can markedly enhance cooling efficiency, thereby increasing output power density and expanding safe operational margins. Most existing reviews concentrate on package-level thermal management, a comprehensive classification and indepth comparison of transistor-level thermal management aimed at the more microscopic heat transfer process inside the device is limited. Therefore, by analyzing the self-heating mechanism of wide and ultra-wide bandgap power semiconductor transistor, this review paper summarizes the strategy of controlling junction temperature  $(T_i)$  from two aspects: junction-to-case thermal resistance  $(R_{th,j-c})$  and power loss  $(P_{loss})$ . Firstly, different sidecooling methods are commented from the junction and bottom heat transfer paths. On this basis, a large number of complex micro/nano interface impediments to heat transfer are discussed, including the mechanism and modulation methods of interface heat transfer. Transistor design methods for optimizing internal electric field (Efield), specific on-resistance  $(R_{on,sp})$ , and switching characteristics are reviewed, which are feasible and effective for optimizing loss and preventing local hot spot generation. Lastly, we discuss the primary challenges in current strategic development and offer guidance for future advancements in transistor-level thermal management. These proven or unproven concepts hold the promise of extremely efficient thermal management, driving leaps forward in (U)WBG power electronics.

#### 1. Introduction

Power electronics systems have made significant advancements in energy efficiency and power density [1,2]. However, as power devices continue to miniaturize, operate at higher frequencies, and integrate more densely, the self-heating effect and associated thermal

management challenges have become increasingly prominent [3–5]. Inadequate heat dissipation can lead to junction temperatures  $(T_j)$  exceeding safe limits, which not only reduces device efficiency but may also lead to device failure, thereby compromising the long-term stability and reliability of the system [6]. Power semiconductor transistors are essential for achieving efficient energy conversion in power electronics

This article is part of a special issue entitled: Micro/Nanoscale Transport published in International Journal of Thermal Sciences.

E-mail addresses: xingm@sdu.edu.cn (G. Xin), caoby@tsinghua.edu.cn (B.-y. Cao).

<sup>\*</sup> Corresponding author. School of Energy and Power Engineering, Shandong University, Jinan, 250061, China.

$<sup>\</sup>ast\ast$  Corresponding author.

systems. Consequently, effective thermal management strategies are critically needed to ensure stable and reliable operation under high-power conditions. Such strategies are vital for minimizing energy loss, reducing carbon dioxide emissions, and promoting the development of more sustainable technologies [7].

Over the past two decades, the emergence of wide band gap (WBG) power transistors, including vertical silicon carbide metal-oxide-semiconductor field-effect transistors (SiC MOSFETs) and lateral gallium nitride high electron mobility transistors (GaN HEMTs), has marked a revolutionary leap in power electronics [8,9]. These WBG-based semiconductors exhibit exceptional electrical properties and robust thermal characteristics, such as high electron mobility and critical field strength. The next frontier in power electronics is anticipated to be led by ultra-wide band gap (UWBG) semiconductors like gallium oxide ( $Ga_2O_3$ ),  $Al_xGa_{1-x}N$ , and diamond, which are poised as potential candidates for the next generation of advanced power technologies [10-15].

UWBG semiconductors, characterized by band gaps ( $E_{\sigma}$ ) greater than 4 eV, maintain higher critical fields ( $E_c$ ) compared to traditional WBG electronics. This property enables them to achieve higher blocking voltages with lower  $R_{on,sp}$  and smaller chip sizes [16,17]. Table .1 outlines the bandgap and thermal conductivity  $(k_T)$  values of various (U) WBG semiconductors. Despite their superior physical properties, (U) WBG electronics pose significant challenges in thermal management due to their extremely high-power densities compared to traditional silicon (Si) electronics. As power electronics, particularly (U)WBG devices, approach the heat dissipation limits imposed by maximum power consumption at the package-level, effective thermal management must evolve from conventional macroscopic approaches to targeted transistor-level strategies that address localized hot spots by prioritizing peak  $T_i$  reduction over average device temperature control. While traditional package-level thermal management relies on macroscopic techniques, such as heat sinks, thermal interface materials, and forced convection, to dissipate heat from the external casing to the ambient environment, these methods are fundamentally constrained by thermal spreading resistance and bulk material limitations, failing to mitigate sub-device thermal gradients and localized nanoscale extreme hotspots, which are critical failure mechanisms in high-power-density semiconductor devices. In contrast, transistor-level thermal management directly focus on microscopic pathways, targets heat generation and dissipation at the semiconductor junction through advanced materials, innovative structural designs, and dynamic power loss optimization, enabling precise heat extraction from active regions, which is a critical capability for (U)WBG devices operating at high-power-density. This paradigm shifts from package-centric to junction-centric thermal management underscores the necessity of integrating both macroscopic and microscopic approaches to fully realize the performance and reliability potential of next-generation power electronics.

Physical characteristics differ between vertical and lateral power transistors due to their distinct transistor architectures. By increasing the thickness of drift region without reducing the transistor size, vertical transistors can lower the  $R_{on,sp}$  and increase the BV [18,19]. Vertical transistors exhibit more uniform heat distribution due to current flow through a larger cross-sectional area. In contrast, lateral transistors conduct current primarily through the surface, increasing the likelihood of local hot spot formation in the thin conductive channel near the surface [20]. Vertical transistors excel in high-power scenarios due to their superior power handling capacity and more straightforward

Table 1 Physical properties of silicon (Si) and major (U) WBG semiconductors. (x = 0.3–0.7 for  $Al_xGa_{1.x}N$ ). Data were adopted from Refs. [9–15].

| Property            | Si   | SiC | GaN  | Ga <sub>2</sub> O <sub>3</sub> | Al <sub>x</sub> Ga <sub>1-x</sub> N | Diamond |

|---------------------|------|-----|------|--------------------------------|-------------------------------------|---------|

| E <sub>g</sub> (eV) | 1.12 | 3.3 | 3.45 | 4.8                            | 3.4-6                               | 5.5     |

| $k_T$ (W/m K)       | 150  | 370 | 130  | 11-27                          | 8.8–9.7                             | 2400    |

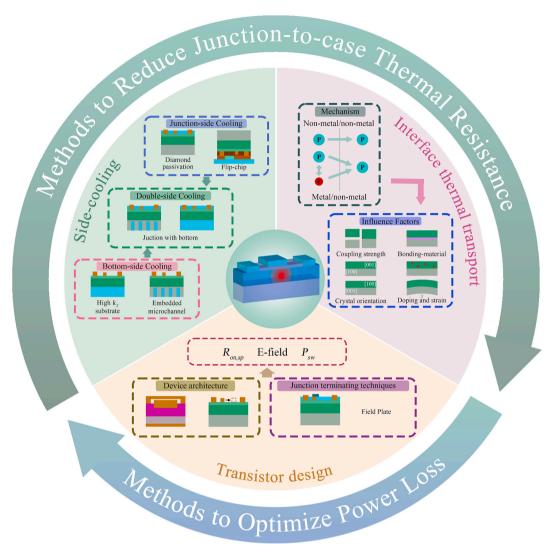

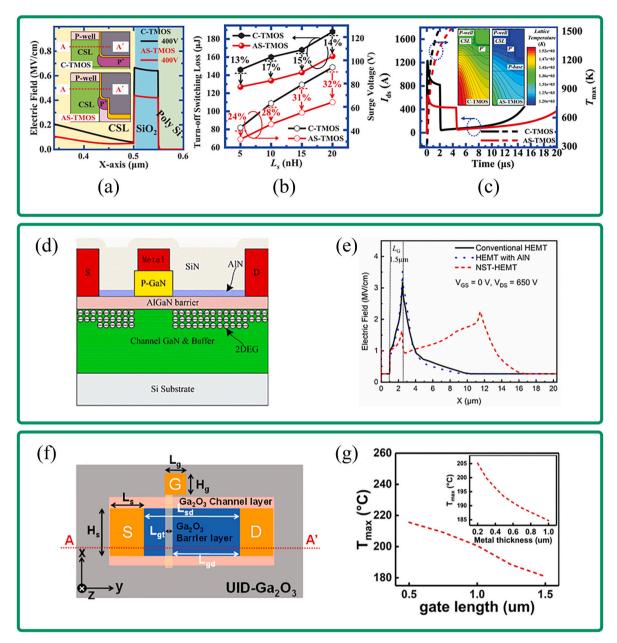

thermal management [21]. SiC MOSFETs exemplify successful vertical power transistors, driving ongoing advancements in other emerging ultra-wide band gap (UWBG) vertical transistor technologies. Conversely, lateral transistors offer advantages for applications requiring high frequencies and low power. While lateral GaN HEMTs are relatively mature, they have spurred research into transistor-level thermal management due to their low  $k_T$  substrate and complex multilayer thermal boundary resistance (TBR) [22]. Ga<sub>2</sub>O<sub>3</sub> and Al<sub>x</sub>Ga<sub>1-x</sub>N, as prominent UWBG semiconductors, are primarily investigated in lateral transistor configurations. These materials exhibit extremely low  $k_T$ , intensifying the self-heating effect and necessitating efficient heat dissipation strategies. Diamond stands out due to its exceptionally high  $k_T$ , offering significant potential for effective heat dissipation applications. Recent advances in transistor-level thermal management have significantly advanced the fundamental understanding of this critical field, as evidenced by several insightful reviews [6,23-26]. However, the rapid development of (U)WBG semiconductor technology has introduced new challenges in managing the intricate electro-thermal interactions spanning multiple scales. To address these emerging demands, this review introduces a comprehensive electro-thermal co-design framework that systematically unifies thermal resistance reduction with power loss optimization for effective  $T_i$  control in (U)WBG devices. Departing from conventional methodologies, our analysis offers: (1) A holistic evaluation of thermal management strategies across diverse heat transfer pathways; (2) A critical assessment of interfacial phonon scattering mechanisms and their role in thermal regulation; (3) Systematic connections between nanoscale thermal transport phenomena and device-level electrothermal performance. By integrating material insights with transistor design principles, this work offers transformative strategies that transcend traditional limitations of material-centric or package-focused thermal management in high-power electronics. The central objective of transistor-level thermal management outlined in this review is to reduce  $T_i$  starting with junction-to-case thermal resistance  $(R_{th,i-c})$  and  $P_{loss}$ . Fig. 1 presents a comprehensive overview of the key strategies employed in transistor-level thermal management, including reducing  $R_{th,i-c}$  through side-cooling and interface thermal transport, and optimizing  $P_{loss}$  through transistor design.

In reviewing techniques to reduce the  $R_{th,j-c}$  of power transistors, various heat transfer paths and interfacial heat transfer mechanisms have been considered. Specific strategies are employed in each method to enhance the thermal performance of device. Top-side cooling focuses on enhancing direct heat transfer from the transistor junction to the package, thereby mitigating thermal limitations, such as the low  $k_T$ observed in materials like Ga<sub>2</sub>O<sub>3</sub> [27]. Despite its effectiveness, top-side cooling may be constrained by the heat dissipation area of the electrode. Bottom-side cooling in power transistors leverages a substrate with high  $k_T$  or incorporates embedded microchannels to enhance heat dissipation. This approach capitalizes on the larger surface area of the substrate to efficiently dissipate heat generated within the transistor, thereby reducing the  $R_{th,i-c}$  [28]. Combining both top-side and bottom-side cooling approaches, double-side cooling offers comprehensive thermal management. By integrating multiple heat transfer paths, this method optimizes heat dissipation across the entire transistor structure [29–31]. The transistor is a complex structure composed of multiple layers, including semiconductors, metals, and dielectric materials. Within this structure, interface heat transport plays a significant role in determining the  $R_{th,i-c}$ . TBR or thermal boundary conductivity (TBC), which are inversely related, are commonly utilized to denote the heat transfer capacity at the interface between different materials or layers within a transistor. High TBR values create bottlenecks in interfacial heat transfer, thereby limiting the overall heat dissipation efficiency and potentially compromising the performance and reliability of transistors. Therefore, enhancing interface heat transport and minimizing TBR are critical scientific and technical challenges in the field of power transistor heat dissipation. As another focus of transistor-level thermal management, transistor design has a major impact on both electrical

Fig. 1. Schematic of transistor-level thermal management in (U)WBG power semiconductor transistors.

performance and thermal management [32].  $P_{loss}$  is minimized through transistor design, consequently leading to a significant reduction in heat generation. Optimizing of the  $P_{loss}$  can be achieved by reducing  $R_{on,sp}$ , alleviating E-field congestion and improving switching characteristics through improved transistor design. To achieve thermo-electric co-design, it is crucial to ensure that thermal management does not compromise the essential performance of the power transistor.

This review focuses on the transistor-level thermal management of (U)WBG power semiconductor transistors. The present situation and challenges of transistor-level thermal management are analyzed from the perspective of  $R_{th,j-c}$  c and  $P_{loss}$ . The article is structured as follows: section.2 analyzes the self-heating mechanism and thermal resistance ( $R_{th}$ ) network of typical power transistors; section 3 reviews the methods and research status of side-cooling; section 4 discusses the mechanism and modulation methods of interface thermal transport; section 5 reviews the current research status of transistor design as a method for transistor-level thermal management; section 6 discusses the existing challenge and future prospects of transistor-level thermal management of (U)WBG electronics; section 7 provides a summary of the article.

#### 2. Thermal analysis of power semiconductor transistors

With the ongoing advancement in electronic devices, the power density continues to increase, leading to local heat flux densities of  $1 \text{ kW/cm}^2$  or higher, thereby elevating local temperatures [33,34]. This

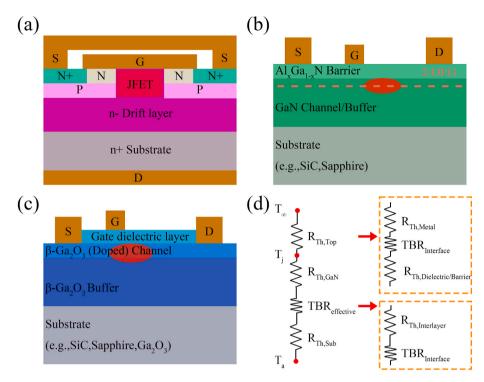

phenomenon significantly impacts the performance and operational reliability of electronic devices. In the absence of efficient thermal management techniques, the self-heating of electronic devices intensifies. (U)WBG electronics feature larger bandgaps, which help mitigate uncontrolled carrier conduction induced by elevated thermal energy. However, higher  $T_i$  can compromise ohmic and gate contacts [23]. Moreover, severe internal overheating diminishes charge carrier mobility, thereby reducing output power and increasing gate leakage current [35–37]. Therefore, to meet the demands of high-power density environments, implementing advanced thermal management techniques is imperative. The primary objective of effective thermal management strategies is to comprehend the underlying physical mechanisms of (U)WBG self-heating. Fig. 2 illustrates the fundamental transistor structures of a vertical SiC MOSFET [38], a lateral GaN HEMT [39], a lateral  $Ga_2O_3$  MOSFET [40], and the  $R_{th}$  network of power transistors.

In Fig. 2 (a), the typical SiC MOSFET utilizes a PN junction formed by a doped P-base region and a lightly doped N-drift region to block voltage. When the channel opens, electrons flow through the JFET region created between the two P-base regions into the drift region [41, 42]. The peak  $T_j$  is consistently observed in the JFET region of planar gate MOSFETs, located beneath the gate oxide layer [43]. Research into vertical power transistors based on other (U)WBG semiconductors is actively pursued to fulfill the demands of high voltage (>1 kV) and high current (>100 A) applications [44,45].

Fig. 2. Schematic of (a) a SiC MOSFET, (b) a GaN HEMT, (c) a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and (d)  $R_{th}$  network of power transistors.

Recent research in emerging semiconductors has prominently featured lateral transistors, with GaN HEMTs being among the most well-developed. A traditional GaN HEMT typically comprises a substrate, GaN buffer, and AlGaN barrier, as depicted in Fig. 2 (b). Control of the channel switch is achieved through modulation of the gate voltage. The polarization effect at the interface between the GaN buffer and the AlGaN barrier induces a high concentration of two-dimensional electron gas (2DEG). The hot spots in the 2DEG channel become more concentrated while bringing high current density [46-48]. Ga<sub>2</sub>O<sub>3</sub> MOSFETs share a structural similarity with GaN HEMTs, but they incorporate a metal oxide insulator (dielectric layer) separating the source and drain. To establish ohmic contact between the electrode and the semiconductor, heavily doped N-type regions are positioned beneath the source and drain. These regions exhibit significantly higher electron concentrations compared to surrounding areas [49]. The peak  $T_i$  occurs in the submicron region near the gate drain edge channel, where a Ga<sub>2</sub>O<sub>3</sub> MOSFET experiences highly localized power consumption and heating during transistor operation [50,51].

Determining the primary factors influencing  $T_j$  is crucial for devising effective thermal management strategies. The following formula can be employed to calculate  $T_j$  for a power transistor operating at room temperature ( $T_a$ ):

$$T_{i} = (R_{th,i-c} + R_{th,c-a})P_{loss} + T_{a}$$

$$\tag{1}$$

where  $R_{th,c-a}$  is the thermal resistance of the case to the ambient, which can be optimized by advanced packaging technology. Analyzing the formula, effective measures for transistor-level thermal management involve reducing  $R_{th,j-c}$  and optimize  $P_{loss}$  under certain  $T_a$  and packaging process.

Based on the  $R_{th}$  network model in Fig. 2 (d), heat transfer occurs via two main thermal pathways. The  $R_{th,j-c}$  primarily encompasses the semiconductor material, substrate material, metal electrodes and their intricate interfaces. Effectively reducing  $R_{th,j-c}$  requires focused efforts on two key aspects: side-cooling and enhancing interface thermal transport. Currently, widely used low-cost substrates such as Si and sapphire constrain the performance enhancement of (U)WBG transistors due to their low  $k_T$  [52]. For Ga<sub>2</sub>O<sub>3</sub>, despite its advantages in terms of

UWBG and economic benefits from melt growth techniques [53,54], its exceptionally low  $k_T$  exacerbates self-heating effects. Additionally, the complexity of interfaces and strong phonon boundary scattering significantly contribute to high TBR, thereby impeding efficient heat transfer [55–60].

$P_{loss}$  is another critical factor affecting  $T_j$ , which can be considered as the total power loss ( $P_{t,loss}$ ) and the local power loss (power loss per unit volume,  $P_{v,loss}$ ). For unipolar transistors, the total power loss ( $P_{t,loss}$ ) is the sum of conduction loss ( $P_{con}$ ) and switching loss ( $P_{sw}$ ) [3,61]:

$$P_{t,loss} = P_{con} + P_{sw} = DR_{on,sp} \frac{I_0^2}{A} + fk_s A$$

(2)

where D is the duty cycle, A is the chip area,  $I_0$  is the conducting current, f is the switching frequency,  $k_s$  is a circuit-related switching parameter. In the process of electronic miniaturization and high frequency,  $R_{on,sp}$  and switching characteristic plays a direct role in  $P_{t,loss}$ . Lowering the  $R_{on,sp}$  and improving the switching characteristics effectively reduce the  $P_{t,loss}$  of the transistor through specific transistor design optimizations [62].

When a voltage is applied to a vertical transistor, the E-field distributes evenly throughout the transistor, unlike in lateral transistors where E-field spikes can occur at the gate edge [63,64]. This characteristic contributes to vertical transistors having a more uniform heat distribution compared to lateral transistors, as a uniform thermal field is often associated with a uniform E-field distribution. During current flow between the source and drain, the carrier density is very high. Collision energy loss between electrons and the lattice results in self-heating [65–67]. The energy transferred by electrons to the lattice is composed of [67]:

$$P_{v.loss} = nev_d(E)E \tag{3}$$

where n is the electron density, e is the charge of the electron, and  $v_d(E)$  is the field dependent drift velocity [68], and E is the E-field intensity. Therefore, the uniform E-field helps prevent local high-power density caused by peak E-field spikes and mitigates the formation of extreme hot spots. Designing transistors with strategies aimed at dispersing charge

density can further alleviate hot spots associated with E-field accumulation [3]. By implementing appropriate design measures, engineers can achieve more uniform E-field and heat distribution within the transistor [69,70]. In summary, transistor-level thermal management necessitates integrating thermal considerations into the transistor design from the outset of its development process. This proactive approach ensures that thermal effects are effectively managed, thereby enhancing the overall performance, reliability, and longevity of electronic devices.

#### 3. Side-cooling in transistor-level thermal management

During the operation of a power transistor, the heat generated in the active region disperses outward through two primary paths: from the top (junction) and from the bottom. Integrating high  $k_T$  materials on both sides of the power transistor can effectively reduce the  $R_{th,j-c}$ , thereby inhibiting heat accumulation. In addition, in areas with strong operability, such as the substrate region, introducing liquid to promote heat exchange with the active region of the transistor represents a proactive approach to heat dissipation. This section will explore side cooling strategies in transistor-level thermal management, encompassing junction-side cooling, bottom-side cooling and double-side cooling.

#### 3.1. Junction-side cooling

Given that hot spots in power transistors typically manifest closer to the transistor junction, effective heat extraction from the top of the transistor becomes crucial. Junction-side cooling methods rely on layers above the channel, such as AlGaN, passivation materials, and gate insulators, rather than the costly substrate material. Junction-side cooling generally encompasses three primary approaches: diamond passivation, two-dimensional (2D) material radiator, and flip-chip integration.

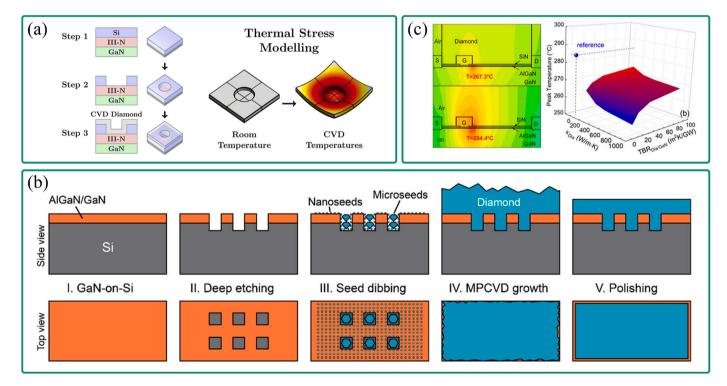

#### 3.1.1. Diamond passivation

Due to the high  $k_T$  and excellent insulating properties of diamond materials, integrating diamond as a passivation layer atop the transistor can significantly improve the thermal dissipation of hotspots to the surface, thereby reducing  $T_i$ . Diamond passivation emerged as a pioneering method validated initially on GaN HEMTs, showcasing its competitiveness in thermal management applications. However, the bond between diamond and GaN is inherently weak and lacks a feasible covalent Ga-C bond. A notable challenge encountered in the direct growth of diamond on GaN using CVD arises from the weak interface and the thermal expansion coefficient disparity between these two materials. Specifically, GaN exhibits a higher thermal expansion coefficient at room temperature (5.59  $\times$  10<sup>-6</sup> K<sup>-1</sup>) compared to diamond  $(4.38 \times 10^{-6} \text{ K}^{-1})$ . This difference results in considerable stress and strain at the interface during temperature variations, which can potentially lead to structural damage or delamination. Cuenca et al. [71] conducted research on the thermal stress of CVD diamond films integrated with GaN, as shown in Fig. 3 (a). During the heating phase, internal stresses within the diamond film cause deformation, influencing the final structure upon subsequent cooling to room temperature. The researchers suggest that prestressing the film before growth could potentially mitigate these thermal stresses and improve the integrity of the diamond-GaN interface. Building upon these findings, Arivazhagan et al. [72] proposed a new structure in where the PCD layer is selectively deposited on the drain rather than directly on the transistor channel. Technology Computer Aided Design (TCAD) analysis demonstrated that this approach, compared to traditional GaN-on-Si HEMTs, reduces self-heating effects and enhances saturated drain current. Fig. 3 (b) depicts a method of seeding diamond with both micro- and nano-seeds proposed by Soleimanzadeh et al. [73]. This approach offers improved crystallinity, larger grain size, and superior interface coverage compared to conventional nano-seeding methods. Consequently, it achieves a

Fig. 3. (a) Approaches to diamond on GaN/III-N integration using membrane fabrication. The GaN/III-N membrane numerical model of the displacement field in micrometres (z scale 10 for visibility) at the beginning of microwave plasma assisted CVD growth [71]. (b) Schematic diagram of diamond-on-GaN substrate fabrication using the seed dibbling method: (I) GaN-on-Si substrate, (II) deep etching of holes, (III) seed dibbling using both nano- and microseeds of diamond, (IV) microwave plasma chemical vapor deposition (MPCVD) diamond growth, and (V) diamond polishing (Copyright © 2021, American Chemical Society) [73]. (c) The thermal distribution of devices with and without a diamond heat spreader across the active region at a power density of 15 W/mm (left); The peak temperature of the device as a function of the  $k_T$  of diamond and the TBR between diamond and GaN (right) [74].

two-fold increase in  $k_T$  of GaN-on-Si with just a 20  $\mu$ m thick diamond layer. Wu et al. [74] studied the effect of diamond thermal conductive sheet on the actual thermal performance of the device, and simulated the device using the thermal properties extracted by time-domain thermal reflection (TDTR). Fig. 3 (c) illustrates the thermal distribution of devices with and without a diamond heat spreader, revealing a temperature difference of 17.1 °C between the two methods. Hao et al. [75] deposited a smooth nano-diamond film with high thermal conductivity on the GaN surface. The high crystallinity of the NCD film results in a low TBR (12.8  $\pm$  0.64 m<sup>2</sup> K/GW) and high thermal conductivity (200  $\pm$  40 W m<sup>-1</sup>K<sup>-1</sup>) for the entire NCD layer. Notably, when the thickness of the top diamond film is restricted, the improvement of TBR has more significant effect on the heat transfer at the top than the improvement of diamond  $k_T$ . The issue of TBR will be discussed in section.4.

The superior thermal performance of PCD passivation layers has been successfully demonstrated in GaN transistors, prompting interest in its application to  $\rm Ga_2O_3$  transistors as well. Given the low  $k_T$  of  $\rm Ga_2O_3$ , the effectiveness of PCD passivation layers becomes particularly critical for managing heat dissipation during high-frequency operations. Yuan et al. [31] demonstrated the effectiveness of employing a high  $k_T$  (400 W/K) film on top of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor through thermal simulations. The rapid extraction and transfer of heat to the source and drain metals can reduce the maximum  $T_j$  by 26 %. Malakoutian et al. [76] achieved successful growth of PCD on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> using CVD for the first time. The PCD/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface was smooth, with the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate remaining undamaged. They measured the TBR of the PCD/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface to be 30.2  $\pm$  1.8 m<sup>2</sup> K GW<sup>-1</sup>, representing a significant advancement in junction-side cooling strategies for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronic transistors. The impact of the PCD passivation layer thickness on the

channel temperature was investigated by Kim et al. [77]. For the PCD passivation layer at 267 nm thick, the effect of TBR on the temperature rise of the channel was negligible. However, for 1  $\mu$ m and 2  $\mu$ m thick PCD layers, the steady-state temperature rise varied by approximately 8% and 18%, respectively, across different TBR values. In a recent work, nanocrystal diamond (NCD) deposited via microwave plasma enhanced chemical vapor deposition (MP-CVD) by Masten et al. [78] as a Junction-side cooling solution for lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors. The addition of NCD thermal diffusion layer reduces the total gate thermal resistance of heterogeneous FET by 42%. Generally, achieving high interface quality and employing mechanical-based methods to reduce TBR at the diamond passivation layer interface are crucial for maximizing heat dissipation advantages [79].

#### 3.1.2. 2D material radiator

Coupled radiators play a pivotal role in high-power semiconductor electronics by significantly expanding the heat exchange area, thereby enhancing heat dissipation efficiency. The 2D structure and large surface to volume ratio of graphene make it and its related 2D materials ideal for heat dissipation [80,81]. Balandin et al. [82] pioneered the application of graphene-based heat spreaders for cooling GaN HEMTs. Fig. 4 (a) illustrates the concept of using graphene-graphene as a top surface heat spreader. In Fig. 4 (b), simulations depict the temperature distribution with and without a graphene-based heat spreader in AlGaN/GaN HEMTs, demonstrating a potential reduction of approximately 20 °C in hot spot temperatures for transistors operating at around 13 W/mm. This approach introduces a novel category of materials for localized heat propagation, maintaining superior thermal properties at the nanoscale and representing a revolutionary advancement in thermal management

Fig. 4. (a) Schematic of the graphene-based heat heat spreaders attached to the drain contact of the AlGaN/GaN HEMT. (b) Temperature distribution in AlGaN/GaN HFET without (top) and with (bottom) the heat spreader [82] (c) Thermally optimized diamond-incorporated flip-chips configuration. (d) Thermal optimization process of the flip-chip integration scheme (*Copyright* © 2021, *IEEE*) [91].

strategies. Subsequently, researchers employed Au/Pt/Ti micro coil test structures to evaluate the effectiveness of graphene as a heat spreader [83-85], highlighting its capability for efficient heat dissipation. However, the zero-band gap of graphene necessitates passivation through  $SiO_2$  (a low  $k_T$  material) between hot spots, which partially impedes heat transfer. Hexagonal boron nitride (hBN), another 2D material with thermal properties akin to graphene, can act as a 2D insulating heat spreader in direct contact with hot spots [86–88]. Choi et al. [86] found that a 35 nm thick layer of h-BN on a glass substrate was sufficient to reduce the hot spot temperature by 4.1 times. Nazim et al. [87,88], in their studies using Au/Pt/Ti micro-coil test structures, investigated the heat dissipation capabilities of h-BN. They concluded that a multilayer h-BN, approximately 2 nm thick, is optimal and sufficient for effective heat dissipation through direct contact. Due to their outstanding properties, 2D materials hold significant promise for enhancing heat dissipation in power electronics, offering prospects for integration into future applications in power electronics.

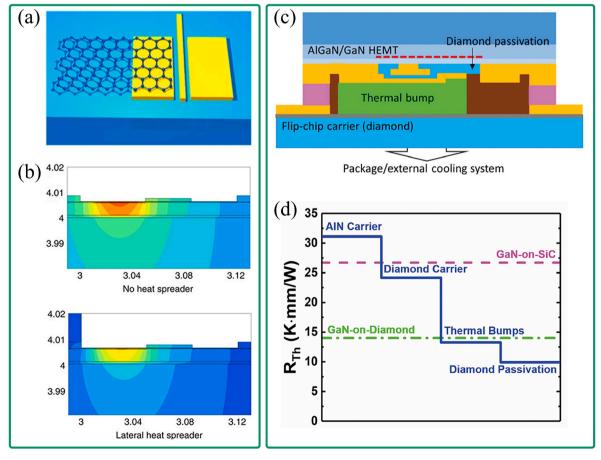

#### 3.1.3. Flip-chip integration

Flip-chip integration represents a competitive method for junctionside cooling, proven to significantly reduce transistor  $R_{th,i-c}$  to manageable levels [89–91]. Lundh et al. flip-chip integrated AlGaN on sapphire onto a diamond carrier [89], achieving a remarkable 78 % reduction in  $R_{th,i-c}$  through the use of gold thermal bumps. In flip-chip configurations, the thermal bump is typically positioned between the transistor and the carrier wafer to enhance heat extraction from the top. Chatterjee et al. [90] used simulations to demonstrate that incorporating a 2  $\mu m \times 100$ µm thermal bump above the channel region adjacent to the gate in  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> FETs could further reduce  $\Delta T_i$  by an additional 12 %. Carriers play a crucial role in facilitating effective flip-chip integration strategies. Shoemaker et al. [91] investigated the use of PCD as a carrier for integrated flip-chip cooling of GaN HEMTs, as shown in Fig. 4 (c). Fig. 4 (d) illustrated the thermal optimization process of the flip-chip integration scheme. By adopting PCD carriers, they achieved a 22 % reduction in  $R_{th,i-c}$  compared to AlN carriers, resulting in approximately 24.15 K mm/W. Through further optimization involving thermal bumps, they achieved a 45.1 % reduction ( $\sim$ 13.25 K mm/W) in  $R_{th,i-c}$ , and an additional 25 % reduction (~9.87 K mm/W) through diamond passivation. This optimized transistor configuration exhibits lower  $R_{th,j-c}$  than current state-of-the-art GaN-on-diamond HEMTs. In the heat transfer process from the semiconductor material to the metal electrode, TBR between the metal electrode and the semiconductor material plays a significant role [92-94], influencing overall heat transfer efficiency. Additionally, the dielectric layer separating the gate electrode from the channel impacts thermal management, making high-quality and high  $k_T$ dielectric materials preferable [95].

Furthermore, when selecting gate materials for (U)WBG power devices, several critical factors beyond high  $k_T$  must be carefully considered: low leakage, low  $R_{on,sp}$ , high BV, environmental stability, and high crystallization temperature. Optimizing these factors in gate material selection for (U)WBG power devices is critical for achieving high efficiency, reliability, and performance across various applications, including power electronics and high-power applications.

#### 3.2. Bottom-side cooling

Bottom-side cooling is a thermal management technique designed to enhance heat dissipation by transferring heat through the substrate to the package-level heat sink. Leveraging the extensive area beneath the transistor, bottom-side cooling offers significant advantages in heat dissipation compared to top-side cooling. Strategies such as high  $k_T$  substrates and embedded microchannels are widely adopted and have demonstrated effectiveness in improving the thermal performance of transistors. Notably, achieving optimal performance in the combination between a chip and its substrate requires careful co-design considerations for mechanical bonding, electrical bonding, and thermal bonding.

These aspects are crucial for ensuring effective interface thermal conduction, electrical conduction, and mechanical adhesion simultaneously. These approaches have garnered considerable interest among researchers in recent years.

#### 3.2.1. High $k_T$ substrate

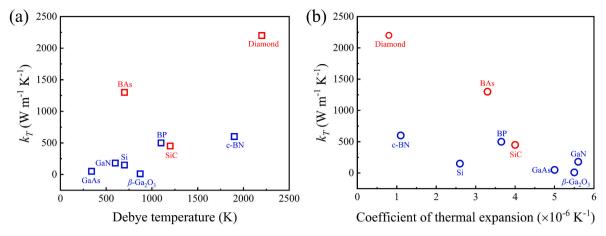

Recently, researchers have been actively pursuing high-conductivity materials to replace conventional substrates in electronic systems for improved cooling efficiency [96–98]. Fig. 5 (a) and (b) compare the  $k_T$ , Debye temperature, and coefficient of thermal expansion of various semiconductor materials alongside high  $k_T$  substrate materials. When choosing a substrate, prioritizing  $k_T$  is essential. Moreover, minimizing the TBR is facilitated by selecting materials with closely matched Debye temperatures and coefficients of thermal expansion between the semiconductor and substrate materials. This approach maximizes the benefits derived from high  $k_T$ . Materials such as SiC, diamond, boron arsenide (BAs), and other high  $k_T$  materials have emerged prominently in this pursuit, prompting extensive theoretical and experimental research efforts [99–103].

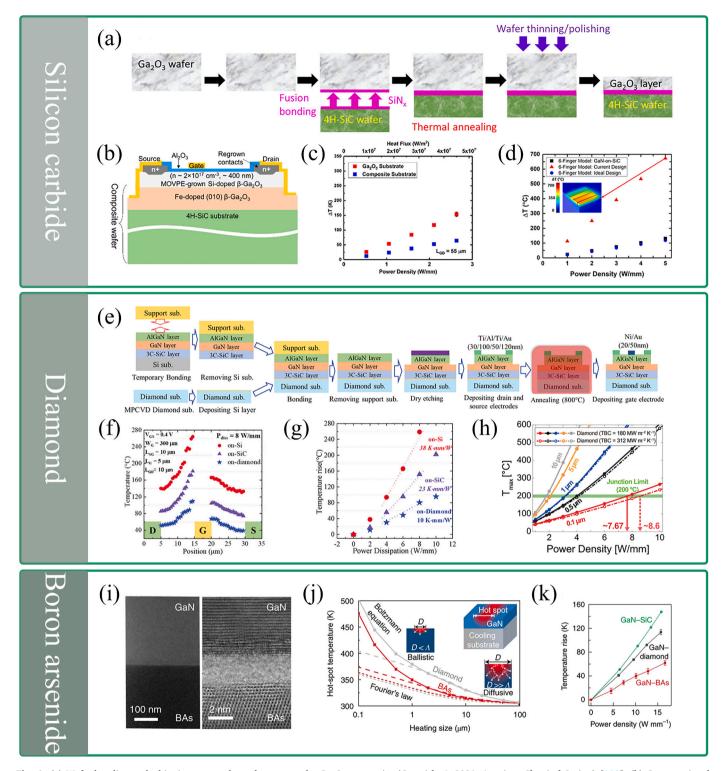

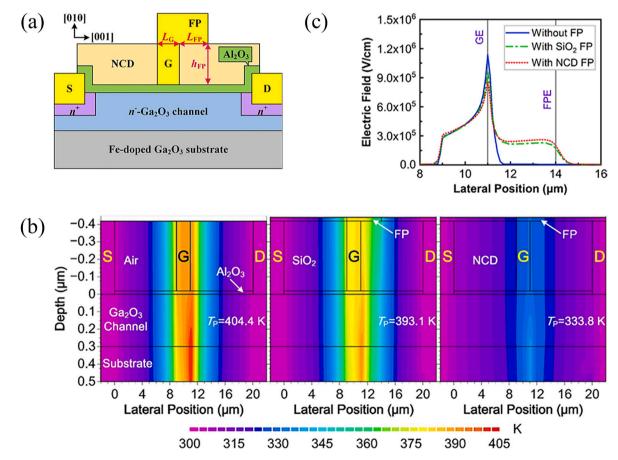

SiC: SiC stands out as a well-established semiconductor material known for its high  $k_T$ , making it highly suitable for use as a substrate material. The relatively minimal lattice mismatch between GaN and SiC results in low dislocation density, rendering GaN epitaxy on SiC particularly attractive [104-106]. Binari et al. [104] were the first to successfully grow AlGaN/GaN HEMT on SiC substrates. Through the continuous efforts of scientists, Feng et al. [105] developed a high-quality GaN film buffer layer with low TBR on SiC, utilizing an ultrathin AlGaN buffer layer with low aluminum content. This ultra-thin buffer layer enhances crystal quality and diminishes TBR at the GaN/SiC interface. Similar cooling techniques employed for GaN can also be applied in Ga<sub>2</sub>O<sub>3</sub>-based transistors, where heat dissipation requirements are more critical. In 2019, Xu et al. [107] achieved the pioneering heterogeneous integration of 2-inch β-Ga<sub>2</sub>O<sub>3</sub> films on 4H-SiC and Si (001) substrates by an ion cutting process. Compared with reported Ga<sub>2</sub>O<sub>3</sub>-on-Ga<sub>2</sub>O<sub>3</sub> transistors, Ga<sub>2</sub>O<sub>3</sub>-on-SiC transistors exhibit excellent thermal stability at operating temperatures up to 500 K, attributed to the high  $k_T$  of the SiC substrate. In related work by the same group, Schottky barrier diodes (SBD) were prepared on β-Ga<sub>2</sub>O<sub>3</sub>/SiC heterostructure material [108], exhibiting a 25 % lower temperature rise at equivalent power levels compared to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers alone. Song et al. [109] reported the fabrication of Ga<sub>2</sub>O<sub>3</sub>/4H-SiC composite wafers through a fusion bonding method, as shown in Fig. 6 (a), achieving successful growth of the Ga<sub>2</sub>O<sub>3</sub> epitaxial layer on the composite substrate. In a subsequent work [110], the same group proposed low-temperature growth axial Ga<sub>2</sub>O<sub>3</sub> transistors (Fig. 6 (b)), with high thermal performance and the highest power (~300 MW cm<sup>-2</sup>) reported to date among heterogeneous integrated Ga<sub>2</sub>O<sub>3</sub> transistors. As illustrated in Fig. 6 (c), due to the enhanced heat transfer performance of the composite substrate, the  $\Delta T_i$  of the transistor operating at a power density of 2.63 W/mm ( $L_{GD} = 55 \mu m$ ) is 2.4 times lower than that of the  $Ga_2O_3$  substrate. Furthermore, the thermal performance of the multi-finger device is examined. Due to thermal cross-talk between adjacent current channels, self-heating is notably intensified. In Fig. 6 (d), a substantial reduction in channel temperature of approximately 8 times is observed in the ideal multi-finger configuration, suggesting potential to lower device  $R_{th}$  below that of current commercial GaN-on-SiC transistors. Recently, Xu et al. [111] used ion cutting and surface-activated bonding techniques to integrate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heterogeneous onto SiC substrates. Combined with thermal modeling, the thermal resistance of Ga<sub>2</sub>O<sub>3</sub>-on-SiC devices is two orders of magnitude lower than that of Ga<sub>2</sub>O<sub>3</sub>-on- Ga<sub>2</sub>O<sub>3</sub> devices. In addition, the research group [112] found that compared with the epitaxial  $Ga_2O_3$  MOSFETs, the  $I_{on}/I_{off}$  degradation of Ga<sub>2</sub>O<sub>3</sub>-SiC MOSFETs was reduced by 1.5 orders of magnitude, indicating great thermal stability. Through additional device packaging, the thermal resistance of Ga<sub>2</sub>O<sub>3</sub>-SiC MOSFETs reached a record low of 4.45 K mm/W.

Fig. 5. (a) Room-temperature  $k_T$  and Debye temperatures of representative semiconductors and high  $k_T$  materials. (b) Room-temperature  $k_T$  and coefficient of thermal expansion of representative semiconductors and high  $k_T$  materials.

Diamond: To further mitigate the thermal limiting effect of power transistors, the integration of power transistors with high  $k_T$  diamond shows great potential [113]. Diamond is currently the leading research prototype high  $k_T$  material for high-performance power electronics cooling. Integrating diamond with semiconductors offers substantial potential to improve heat dissipation capabilities. Chernykh et al. [114] deposited PCD film on a thin functional silicon layer of 'silicon-on-insulator' (SOI) wafer, followed by the growth of a GaN-based heterogeneous structure. This approach mitigates the detrimental effects of high PCD growth temperatures on GaN layer performance. Compared to conventional GaN-on-SiC based HEMTs, the method reduces surface temperatures by more than 50  $^{\circ}\text{C}$  and increases mean time to failure by 2 orders of magnitude. Recently, Kagawa et al. [115] demonstrated the successful transfer of AlGaN/GaN/3C-SiC layers grown on Si to large-size diamond substrates and subsequently fabricated GaN HEMTs on diamond. The transfer and fabrication process of the GaN/3C-SiC/diamond HEMTs using the bonding-first concept is shown in Fig. 6 (e). Remarkably, even after annealing at 1100 °C, no shedding of the 3C-SiC/diamond bonding interface was observed, highlighting its critical role in enabling high-quality GaN crystal growth on diamond substrates. Fig. 6 (f) and (g) illustrate the temperature distribution and the temperature rise with power dissipation ( $P_{\rm diss}$ ) of the GaN HEMTs on the Si, SiC, and diamond. Compared to other structures, GaN-on-diamond exhibits significantly lower  $T_i$ , demonstrating clear thermal superiority. Furthermore, diamond substrates, initially proven effective for GaN applications, have shown promise in the realm of β-Ga<sub>2</sub>O<sub>3</sub> as well. Oh et al. [116] utilized thermal simulation to demonstrate that diamond substrates reduced the lattice temperature of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, consequently mitigating drain current degradation. Matsumae et al. [117] combined the surface functionalized  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with the PCD substrate directly in the atmosphere at 250 °C. The interface structure analysis confirmed atomic-level bonding between the β-Ga<sub>2</sub>O<sub>3</sub> and diamond surfaces, devoid of nanoholes, cracks, or intermediate layers. Recently, Kim et al. employed finite element modeling [118] to analyze the thermal properties of transistors using diamond substrates and submicron-thin  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers. The thermal model of the transistor is depicted in Fig. 6 (h). At a  $T_i$  limit of 200 °C, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor can handle a maximum power density of up to 8.6 W/mm. Gu et al. [119] fabricated Ga<sub>2</sub>O<sub>3</sub>/diamond heterojunctions by the atomic layer deposition (ALD) method, and measured the  $k_T$  of  $Ga_2O_3$  thin films and the TBC of  $Ga_2O_3$ /diamond by TDTR to be 5.13 W/(m·K) and 19.22 MW/(m<sup>2</sup>·K). Lately, Hu et al. [120] designed and realized the fabrication of GaN devices on diamond-SiC composite substrates. Compared with GaN-on-SiC technology when the base temperature is  $T_{base} = 25 \, ^{\circ}C$  and  $P_{diss} = 7.2$  W/mm, the surface temperature of the improved cooling structure is reduced by 52.5 °C and the thermal resistance is reduced by

about 41 %. The epitaxial growth of  $Ga_2O_3$  films on diamond substrate is an active area of research [121–123], with expectations for significant advancements. However, the large lattice mismatch and thermal mismatch between diamond and  $Ga_2O_3$  are responsible for the poor TBR, thereby diminishing the advantages of inherently high  $k_T$  in diamond.

BAs: BAs boasts an impressive isotropic thermal conductivity of 1300 W m<sup>-1</sup> K<sup>-1</sup> [101], coupled with mechanical and thermophysical properties that are highly compatible with power semiconductors. The integration and characterization of BAs with other semiconductor materials are crucial for its potential application in thermal management strategies. Kang et al. [124] achieved a significant milestone by integrating a BAs-cooled substrate with a GaN device, demonstrating experimental measurements of an operational AlGaN/GaN HEMT (Fig. 6 (i)). Fig. 6 (j) assesses the impact of TBR and demonstrates that diamond exhibits a slight advantage in scenarios where TBR (dotted lines) is not included in the simulation. However, upon including TBR in the simulation (dashed lines), it becomes evident that BAs achieves significantly lower hot spot temperatures compared to diamond. Research findings confirm the superior cooling efficiency of BAs, revealing a lower hot spot temperature ( $\sim$ 60 K) compared to diamond ( $\sim$ 110 K) and SiC ( $\sim$ 140 K) under equivalent transistor power densities, as shown in Fig. 6 (k). This enhanced thermal management capability of BAs is attributed to its unique phonon band structure and effective interface matching. Currently, BAs has been limited to laboratory-scale manufacturing and testing due to challenges such as non-uniformity and frequent defects. Within the same BAs sample, the  $k_T$  can vary significantly, ranging from less than 500 to more than 1200 W m<sup>-1</sup> K<sup>-1</sup> [125]. Improving the quality of grown BAs crystals and developing practical, cost-effective manufacturing processes are critical objectives.

Researchers have explored substrate screening methods suitable for different semiconductor devices. Fahdi et al. [126] used machine learning methods to search for promising substrates or radiators to cool  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. These descriptors based on the primitive cells of substrates are easy to calculate after structural optimization, providing a new way to quickly screen potential substrates from large-scale material pools. In addition, etched microchannel structures filled with high  $k_T$  materials are also an alternative thermal management method [127, 128].

#### 3.2.2. Embedded microchannel

In addition to the high  $k_T$  substrate, the integration of embedded microchannel cooling in close proximity to hot spots represents a more promising and efficient thermal management approach [129–132]. Embedded microchannels actively dissipate heat by introducing coolant directly into the transistor's active region, thereby significantly

Fig. 6. (a) Wafer-bonding and -thinning approach used to create the  $Ga_2O_3$  composite (Copyright © 2021, American Chemical Society) [109]. (b) Cross-sectional schematic of a  $Ga_2O_3$  MOSFET fabricated on the composite. (c) Comparison of the temperature rise of the real and ideal 6-finger devices. (d) Steady-state channel temperature rise of the MOSFETs fabricated on the composite substrate and a bulk  $Ga_2O_3$  wafer with  $L_{GD} = 55 \,\mu\text{m}$  (Copyright © 2023, American Chemical Society) [110]. (e) The transfer and fabrication process of the GaN/3C-SiC/diamond HEMTs using the bonding-first concept. (f) The temperature distribution of the GaN HEMTs on the Si, SiC, and diamond at  $P_{diss}$  8 W/mm. (g) The relationships between the temperature rise of the gate edge and  $P_{diss}$  for the GaN HEMTs on the Si, SiC, and diamond [115]. (h) Maximum transistor temperature and power density for single-gate  $Ga_2O_3$  transistors [118]. (i) Cross-sectional SEM (left) and high-resolution TEM (right) images of a GaN-BAs structure, revealing the atomically resolved interface. (j) Simulations of the hot-spot temperatures for the two best thermal conductors (BAs and diamond), as a function of heating size (from 100  $\mu$ m to 100 nm). (k) A plot depicting GaN temperature versus power density, measured via Raman spectroscopy at the drain side, 0.5  $\mu$ m laterally from the T-gate edge [124].

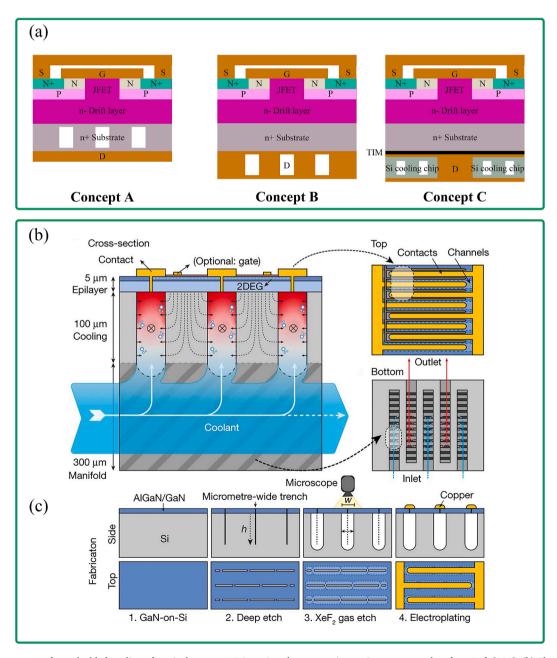

mitigating the self-heating effect. Vertical transistors feature an additional drift layer alongside the channel layer and substrate, allowing for BV scaling by adjusting the thickness of the drift layer without increasing the transistor's footprint [133,134]. This characteristic provides a larger surface area near the drift region, facilitating their application in thermal management strategies [95]. Vadimirova et al. [135] proposed integrating a microchannel cooler within the drift region as a potential solution for vertical power transistors. A number of fluids through-holes perpendicular to the PN junction of the transistor are designed in the drift region. According to their findings from electrical simulations, the electrical performance of the transistor would not be negatively affected. Building upon this foundation, Dede et al. [136] proposed three concepts of embedded cooling for vertical WBG semiconductor transistors, as shown in Fig. 7 (a). These concepts are as follows: A) embedding microchannels directly into the substrate of the power transistor; B) embedding microchannels into the lower electrode of the transistor; Or C) connecting a vertical power transistor to a silicon-cooled chip with microchannels and through silicon via (TSV) via an intermediate metallization plus thermal interface material (TIM) layer. Concept A demonstrates superior heat dissipation performance due to the etched microchannels in the substrate. However, this approach may potentially impact the electrical performance of the transistor by increasing the Ron.sp; Concept B circumvents potential electrical performance issues, yet the deposition/attachment of a thick metal layer and the micromachining required to incorporate microchannels into the lower electrodes pose significant challenges. Concept C utilizes existing Si micro-electro-mechanical systems (MEMS) devices and TSV fabrication techniques. This concept introduces additional TIM and potentially increases the  $R_{th}$ . Jung et al. [137] conducted a detailed exploration of Concept A using one-dimensional thermal fluid modeling. The analysis showed that the temperature of the WBG transistor can be maintained below 200 °C even under a high heat flux of 1 kW/cm<sup>2</sup>. However, achieving low pressure drop in both single-phase and two-phase flows remains challenging due to restrictions imposed by the

Fig. 7. (a) Three concepts for embedded cooling of vertical current WBG semiconductor transistors. Concepts are taken from Ref. [136]. (b) The schematic of the microchannels. (c) The fabrication process of the microchannels [139].

channel height in this embedded cooling technique. On the other hand, the Concept C was thoroughly examined by Zhou et al. [138] using a new jet impact chip cooling structure. A heat flow of up to 1 kW/cm $^2$  can be achieved at a temperature below 177.1  $^{\circ}$ C on average.

For lateral transistors, researchers have primarily explored embedded microchannels targeting the substrate region as an effective method for heat dissipation in GaN transistors [139–144]. Van Erp et al. [139] proposed a monolithically integrated manifold microchannel (mMMC) heat spreader, as shown in Fig. 7 (b). This innovative method enables the extraction of heat flux exceeding 1.7 kW/cm<sup>2</sup> with a minimal pumping power of 0.57 W/cm<sup>2</sup>. Additionally, it predicts that the average additional energy cost for data center cooling could drop below 0.01 percent. Multilayer printed circuit boards (PCBs) are employed to direct coolant into microchannels embedded within semiconductor transistors, ensuring a fully integrated and aligned approach with the electronics to optimize heat dissipation. Fig. 7 (c) illustrates the fabrication process of the microchannels, commencing with anisotropic deep etching through a narrow incision in the AlGaN/GaN film to achieve the required microchannel depth. Subsequent isotropic gas etching completes the formation of the microchannels, thereby integrating transistor design and heat sink fabrication within a unified process. Recently, Nela et al. [140] integrated embedded liquid cooling on a 650 V, 50 m $\Omega$ GaN-on-Si commercial power transistor, demonstrating that embedded liquid cooling has no negative effect on the electrical performance of the transistor. Lian et al. [141] developed a design featuring a high-resistivity silicon (HR Si) interlayer embedded with four microchannels, each with dimensions of 30 µm width and 30 µm spacing. They achieved an average heat dissipation density of 5 kW/cm<sup>2</sup> in the active zone of GaN HEMT using deionized water as the cooling agent at a flow rate of 3 mL/min. Ye et al. [142] embedded the microchannels into the SiC substrate, achieving a gate heat flux of 6349.2 W/mm<sup>2</sup> at a coolant flow rate of 70 mL/min, representing a 1172 % increase compared to traditional remote cooling methods. Zhang et al. [143] proposed an embedded manifold microchannel cooling (EMMC) device, which obtained a high heat transfer coefficient of 105 W/(m<sup>2</sup> K). Lu et al. [144] established a  $R_{th}$  model for embedded HEMT microchannel cooling and observed a reduction of 50  $^{\circ}\text{C}$  in maximum gate temperature and a 43.14 % decrease in  $R_{th,j-c}$  compared to remote cooling methods. The embedded microchannel cooling method has been shown to work well for AlGaN/GaN HEMTs and is expected to shed light on emerging semiconductor materials such as Ga<sub>2</sub>O<sub>3</sub> microchannel cooling. Shuvro et al. [145] pioneered the use of infrared laser etching to embed microchannels in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates for cooling purposes. When the water flow speed is 50 ml/min and the input power of 3.5 W, the surface temperature can be reduced from  $\sim$ 140 °C to  $\sim$ 72 °C. This study offers valuable practical insights into embedded cooling techniques for Ga<sub>2</sub>O<sub>3</sub>

In recent years, research on embedded microchannels has seen significant growth [146–149]. Despite this progress, achieving maximum compactness and highest thermal performance remains a challenge. A primary challenge in the development of next-generation (U)WBG power transistors lies in fabricating microchannels under ultra-thin conditions, typically less than 250  $\mu m$ . Advancements in etching techniques tailored for UWBG materials [150–155] show promise in addressing this challenge. These techniques are crucial for enabling the fabrication of efficient microchannels in such thin substrates. Looking forward, embedded microchannel cooling is expected to emerge as a highly promising active cooling method [150,156] for future semi-conductor devices. Continued research and development in this area will likely lead to enhanced thermal management solutions for high-power electronics.

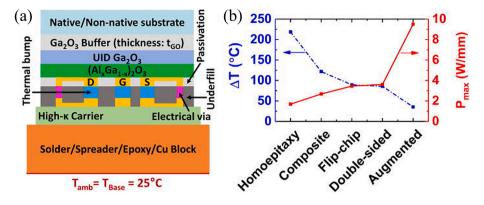

#### 3.3. Double-side cooling

Combining junction-side and bottom-side cooling methods through double-sided cooling presents a robust approach to maximize heat dissipation efficiency in semiconductor devices. Numerical simulations have shown that double-sided cooling of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors can effectively reduce the  $R_{th,j-c}$  to as low as approximately 8.5 mm K/W, which is anticipated to be lower than that achieved with GaN-on-diamond structures [31,91]. In the study of Kim et al. [157], the  $R_{th}$  of the 10 μm thick β-Ga<sub>2</sub>O<sub>3</sub> drift layer accounted for 90 % of the total  $R_{th,i-c}$  of the transistor. The high  $R_{th}$  of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> prevents the heat flow to the bottom, thereby diminishing the cooling effectiveness of costly high  $k_T$  materials like diamond (1000-2000 W/m·K) compared to more common materials such as Cu, AlN, or AlSiC (300-550 W/m·K). Therefore, focusing on enhancing heat dissipation from the junction-side is deemed more effective. Addition of junction-side cooling significantly reduces the maximum temperature of the transistor channel. Compared with bottom cooling, employing double-side cooling reduces the temperature by approximately 50 % for each additional convective heat transfer coefficient value.

Montgomery et al. [95] conducted simulations to assess the impact of junction-side cooling versus double-side cooling on the heat dissipation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical transistors. Double-side cooling is slightly more efficient than top-side cooling (decreasing from 135 °C to 134 °C at 15 MW cm<sup>-2</sup>), leading to the conclusion that even with double-sided cooling, the majority of heat dissipation still occurs through the top due to the relatively low  $k_T$  of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material. Similarly, Chatterjee et al. [90] investigated double-side cooling in a flip-chip integration scheme using a Ga<sub>2</sub>O<sub>3</sub>/4H-SiC composite wafer and arrived at a comparable conclusion. Fig. 8 (a) illustrates the schematic diagram of the double-side cooling scheme. For double-side cooling,  $\Delta T_i$  is only reduced 5 % compared to flip-chip designs. The enhanced double-side cooling design was shown to be able to handle a power density of about 9.5 W/mm at a  $T_i$  limit of 200 °C, as shown in Fig. 8 (b). Kim et al. [74] added a diamond passivation layer on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond for the best heat dissipation performance. The steady-state temperature rise was reduced by approximately 75 % compared to the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs, while also improving transient thermal performance. Notably, configurations with thicker diamond layers on top and thinner  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers exhibited the lowest temperature rise. For applications involving extreme temperatures or high-power densities, (U)WBG transistors, particularly Ga<sub>2</sub>O<sub>3</sub> power transistors, benefit significantly from combined thermal management strategies such as double-side cooling to ensure stable operation.

# 4. Interface thermal transport in transistor-level thermal management

In Section 3, we discuss various heterogeneous integrated transistorlevel thermal management methods. In practical heterogeneous integrated devices, numerous complex micro-nano interfaces impede the heat transport process [158]. Interface thermal transport plays an important role in near-junction heat transport. Due to the acoustic mismatch between the materials, heat carriers encounter difficulties in smoothly transferring across these interfaces, especially in micro- and nano-scale devices. TBR can even be an order of magnitude larger than the inherent  $R_{th}$  of the materials, often becoming a dominant factor impeding heat transport near the junction. In the context of GaN transistors on foreign substrates, TBR has been demonstrated to significantly contribute to the increase of  $T_i$  [159–161]. Given the diverse interface types and intricate energy transfer mechanisms involved in semiconductor transistors, TBR emerges as a central focus in thermal transport research [162,163]. This section examines issues related to interface heat transport in transistor-level thermal management, covering aspects such as interface thermal transport mechanism and influence factors.

#### 4.1. Thermal transport mechanism

Interface atoms differ significantly from bulk atoms primarily

Fig. 8. (a). Schematic of the double-sided cooling scheme. (b)  $\Delta T$  and the maximum power handling capability ( $P_{max}$ ) for the different thermal management schemes [90].

because the local environment at the interface, including interatomic interactions and lattice structures, deviates from that of the bulk region [162]. Achieving a regular and orderly arrangement of local atomic structures at the interface is challenging due to lattice parameter mismatches, atomic misalignments, and different atomic bonding [164]. Additionally, interfaces composed of different materials or phases of the same material exhibit distinct energy states for thermal carriers (such as electron bands and phonon dispersion) on both sides [165]. Overall, understanding and controlling the atomic structure, interatomic interactions, and energy states at interfaces are crucial for optimizing thermal management in semiconductor devices. Addressing these

interface-related challenges is essential for improving heat dissipation and overall device performance.

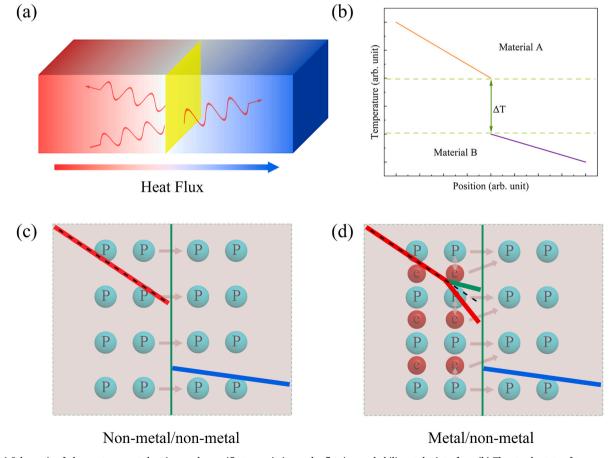

As depicted in Fig. 9 (a), during the process of energy transfer involving heat carriers across the interface, partial transmission and partial reflection back could occur. The disorder of the atomic structure and the mismatch in energy states lead to a significant temperature jump observed at the interface, which fundamentally constitutes TBR, as shown in Fig. 9 (b). The heat in the solid is mainly carried by various carriers such as electrons, phonons, magnetons, and 3He quasi particles in different forms of condensed matter. The research focus of this review centers on power transistors, particularly emphasizing the interfaces

**Fig. 9.** (a) Schematic of phonon transport showing mode-specific transmission and reflection probability at the interface. (b) The steady state of temperature profile for interface. Schematic of heat carrier transmission at (c) Non-metal/non-metal interface and (d) Metal/non-metal interface. The dotted line represents fitting temperature ( $T_{fit}$ ), the red line represents phonon temperature ( $T_{ph}$ ), the blue line represents cooling temperature ( $T_{c}$ ), and the green line represents electron temperature ( $T_{e}$ ). (For interpretation of the references to color in this figure legend, the reader is referred to the Web version of this article.)

crucial to their operation. These interfaces include the dielectric/semiconductor interface, substrate/semiconductor interface, and metal/semiconductor interface, which have been identified as prominent research areas [162,166]. Based on the types of heat carriers involved, these interfaces can be classified into two main categories: non-metallic/non-metallic and metal/non-metallic interfaces, as shown in Fig. 9(c) and (d).

**Non-metal/non-metal:** For non-metal/non-metal interfaces, phonons serve as the primary carriers of heat, depicted in the accompanying Fig. 9 (c). Studies investigating the thermal properties of these interfaces, where phonons dominate heat transfer, typically employ models such as the acoustic mismatch model (AMM) and diffuse mismatch model (DMM) [167–169]. Detailed explanations of AMM and DMM, along with other associated research methodologies, exceed the scope of this review. Ma and Li et al. [170,171] utilized the AMM and DMM models to analyze the thermal transport characteristics at interfaces between  $Ga_2O_3$  and various substrate materials. Ma et al. [170] demonstrated that the difference in TBC between various interfaces

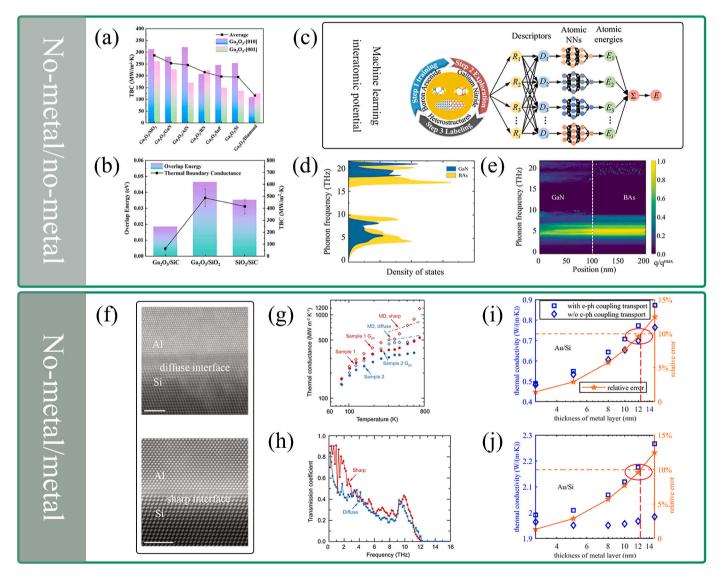

arises primarily from impedance mismatch and variations in phonon density of states (PDOS). The higher TBC observed at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface compared to the Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface primarily stems from the significantly greater transmission function at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface in contrast to the Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface. Li et al. [171] analyzed the heat transport mechanism at the interface in detail, focusing on PDOS and phonon participation ratios (PPR). Figure.10 (a) presents the simulated TBC, while Figure.10 (b) illustrates the overlap energy between materials at different interface regions. Their findings indicate that increased overlap energy enhances phonon heat transfer, thereby boosting PPR at the interface and influencing phonon-phonon interactions. AMM and DMM were developed on the basis of continuum theory, which ignored the detailed atomic structure of materials, thereby limiting their ability to accurately predict TBR or TBC in many cases. In contrast, several numerical methods account for the actual atomic structure of interfaces, such as the lattice dynamics method, atomic green function method, molecular dynamics (MD) simulation, Boltzmann transport equation and Monte Carlo method. Among them,

Fig. 10. (a) TBC for interface between  $Ga_2O_3$  and different substrates, the colorful bars are TBCs along [010] and [001] directions, and the black spots are the average values of them. (b) Relationship between TBC and overlap energy of different interface areas [171]. (c) The basic steps of the MLIP. (d) The comparison of phonon density of states between BAs and GaN. (e) The spectral heat flux in GaN-BAs heterostructures, where the dash line indicates the interface and the color indicates the normalized density of heat flux [173]. (f) Cross-sectional TEM image of Al/Si with diffuse interface (top) and sharp interface (bottom). Scale bars are 2.5 nm. (g) Calculated thermal conductance of sharp (red dashed line) and diffuse (blue dashed line) Al/Si interfaces. (h) Phonon transmission coefficient for sharp (red) and diffuse (blue) interfaces [179]. Overall thermal conductivity of metal/semiconductor bilayer films of Au/Si by keeping thickness of Si layer at (i) 10 nm and (j) 50 nm [180]. (For interpretation of the references to color in this figure legend, the reader is referred to the Web version of this article.)

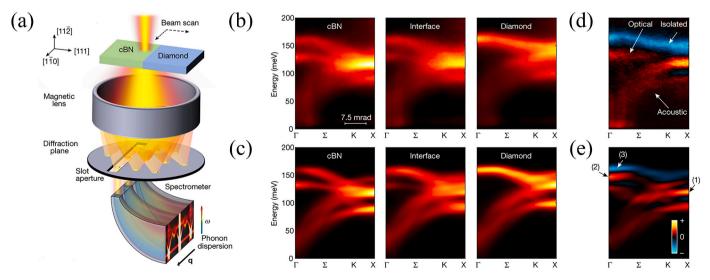

MD simulation is particularly prominent as it offers a comprehensive in-situ approach to investigate interface phenomena in nanomaterials without these limitations.MD simulation rely on precise atomic potentials, which have been significantly enhanced in recent years by the emergence of machine learning interatomic potentials (MLIP) [172-175]. Wu et al. [173] employed neural network potentials (NNP) to develop precise and efficient MLIP of GaN/BAs. Figure.10 (c) outlines the fundamental steps of MLIP. They conducted multi-scale simulations of GaN/BAs heterogeneous structures, achieving an ultra-high TBC of  $260 \text{ MW m}^{-2} \text{ K}^{-1}$ , closely matching experimental findings. The PDOS for GaN and BAs, along with the heat flux at the heterostructure interface, were calculated, as shown in Fig. 10(d) and (e). The extensive overlap in the PDOS suggests a strong correspondence in lattice vibrations between GaN and BAs, indicating favorable matching. Moreover, the interface exhibits a well-matched low-frequency heat flux, further underscoring the compatibility between these materials at the atomic level. The analysis shows that the underlying mechanism is rooted in the harmonious lattice vibrations of BAs and GaN. Sun et al. [175] utilized NeuroEvolution Potential (NEP) to construct a MLIP for β-Ga<sub>2</sub>O<sub>3</sub>/diamond heterogeneous structure with high accuracy. Their study highlighted the influence of state vibration density and interface structure on TBR at the interface. The utilization of MLIP effectively connects simulation outcomes with experimental findings, thereby encouraging further investigation into the mechanisms governing interfacial heat transfer.

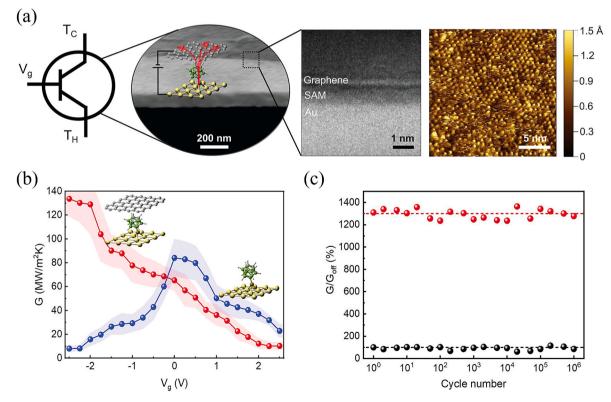

Metal/non-metal: For metal/non-metal interfaces, where heat conduction involves both electrons and phonons, there exist three primary types of thermal carrier interactions: electron-phonon coupling in metals, electron-phonon coupling at the interface, and phonon-phonon interaction at the interface, as shown in Fig. 9 (d) [176,177]. Consequently, the TBR at the interface resembles a network of  $R_{th}$  that needs to be calculated. On the metal side, heat transport involves both electrons and phonons, influenced by temperatures  $T_e$  and  $T_{ph}$  respectively. Conversely, on the non-metal side, heat conduction is primarily governed by phonons, characterized by temperature  $T_c$ . In the past period, researchers have conducted extensive research on the heat transport mechanism at the metal/semiconductor (metal/non-metal) interface [178–180]. Cheng et al. [178] conducted a comprehensive investigation of interfacial heat transport at epitaxial (111) Al/(0001) sapphire interface characterized by exceptionally high quality (atomically sharp, harmonically matched, and ultra-clean). It is found that elastic phonon scattering dominates the heat conduction at the Al-sapphire interface. Inelastic phonon scattering and electron-phonon coupling effects within the metal and at the interface were found to be negligible. Their analysis estimated that electron-phonon coupling contributes approximately 13.6 % to the total  $R_{th}$ . In a similar vein, Li et al. [179] studied the interfacial heat transport of two materials (Al/Si, Al/GaN) characterized by similar Debye temperatures, and found that a large part of phonons would be inelastic transferred on their interfaces at elevated temperatures, significantly improving the TBC. Furthermore, the study examines the correlation between interface quality and  $k_T$ , presenting distinct sharp and diffused interfaces as depicted in Fig. 10 (f). Figure.10 (g) illustrates the  $k_T$  predicted by MD at elevated temperatures. revealing that the TBC at the diffused interface is lower compared to that at the sharp interface. To provide further insight into the observed temperature-dependent thermal conductance, spectral phonon transmittance was calculated using the atomic green function, as illustrated in Fig. 10 (h). The sharpness of the interface critically influences phonon transport dynamics: atomically sharp interfaces facilitate inelastic phonon transport, whereas diffused interfaces hinder such transport. Notably, in practical GaN lateral device architectures, metallic contacts inherently form interfaces with the AlGaN layer. This configuration necessitates urgent investigation into the thermal transport properties at metal/AlGaN interfaces, as their characteristics critically influence device thermal and electrical performance. In related work, Miao et al. [180] simulated heat transport in metal/semiconductor multilayers and identified a critical thickness for the metal layer, as shown in Fig. 10(i)

and (j). Beyond this critical thickness, electron-phonon coupling within the metal layer becomes significant in heat transport. Shi et al. [93] investigated the thermal transport characteristics at the  $\beta\text{-}\text{Ga}_2\text{O}_3/\text{metal}$  interface, emphasizing the pivotal role of the metal cutoff frequency in thermal conduction at the interface. At the metal cutoff frequency, heat transport does not increase further due to the elastic transport assumption. Interfaces between metals and semiconductors are prevalent in micro- and nano-electronics, where heat transfer mechanisms are complex due to diverse heat carriers involved. Further research is warranted to deepen our understanding of interfacial heat transport mechanisms.

#### 4.2. Influence factors

Heat transport across micro-nano interfaces is intricately linked to the atomic properties of the materials flanking the interface, encompassing aspects such as bonding characteristics, crystal structure, defects, and applied pressure. These factors critically influence the coupling and scattering mechanisms of thermal carriers across the interface, including phenomena like phonon boundary scattering and phonon-electron coupling. The influencing factors and strengthening methods of interfacial heat transport are discussed in terms of interfacial coupling strength, bonding materials, lattice mismatches and defects. These considerations play crucial roles in determining the efficiency and effectiveness of heat transfer across such interfaces in various applications, including microelectronics and nanotechnology. Further exploration and optimization of these parameters are essential for advancing our understanding and improving the thermal management capabilities of micro-nano systems.

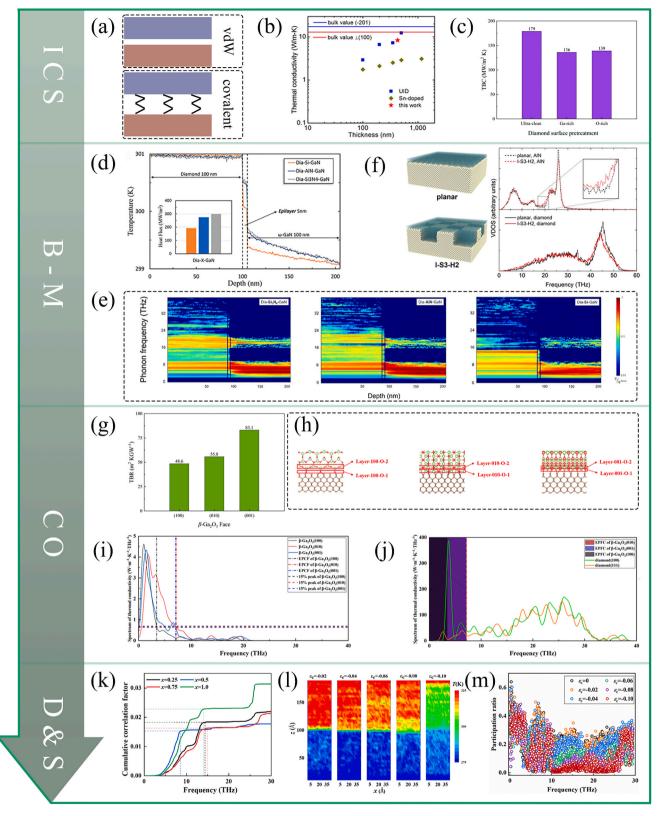

#### 4.2.1. Interfacial coupling strength

The interfacial coupling strength between different materials plays a crucial role in determining interfacial heat transport [162]. This coupling strength is primarily governed by the type of interfacial bonding, which can be divided into van der Waals (vdW) force, hydrogen bond, covalent bond and metal bond [165]. vdW force represents the intermolecular interaction force, hydrogen bonds can occur both intramolecularly and intermolecularly, covalent bonds are strong intramolecular force, and metal bond entails the atomic force. In terms of strength, interfacial bonds rank from highest to lowest as follows: metal bond, covalent bond, hydrogen bond, and vdW force. In transistor applications, the interface connection mode is mainly vdW force and covalent bond (Fig. 11 (a)). The impact of interfacial coupling strength on heat transport across interfaces has been investigated extensively. Cheng et al. [181] achieved the integration of Ga<sub>2</sub>O<sub>3</sub> thin films with diamond through vdW force, resulting in a TBC of 17-1.7/+2.0 MW/m<sup>2</sup>·K (Fig. 11 (b)). Their study highlighted that the TBC between Ga<sub>2</sub>O<sub>3</sub> and diamond is primarily influenced by three key factors: the relatively weak vdW bonding compared to stronger covalent bonds, the limited contact area at the interface, and a significant PDOS mismatch between Ga<sub>2</sub>O<sub>3</sub> and diamond. Subsequently, Ga<sub>2</sub>O<sub>3</sub> was deposited on the single crystal diamond substrate by ALD [182]. The TBC observed at this Ga<sub>2</sub>O<sub>3</sub>-diamond interface was approximately ten times higher than that achieved with vdW bonding (Fig. 11 (c)), underscoring the substantial impact of interface bonding on TBC. So et al. [183] investigated the interfacial heat transport of vdW heterostructures consisting of β-Ga<sub>2</sub>O<sub>3</sub> and h-BN multilayers. After applying strain, the decrease of interfacial distance enhances the interaction between phonons and enhances the interfacial thermal conductance. These findings emphasize that interfacial coupling strength significantly affects thermal transport properties, with stronger bonding mechanisms leading to higher TBC.

#### 4.2.2. Bonding-materials

The incorporation of a phonon spectrum intermediate layer and the introduction of nanostructures at heterogeneous interfaces are crucial strategies for reducing TBR [184–192]. Such bonding-materials serve as

Fig. 11. (a) Diagram of vdW interface and covalent bond interface. (b) TBC of  $Ga_2O_3$ /diamond vdW interface [181]. (c) TBC of  $Ga_2O_3$ /diamond covalent bond interface [182]. (d) Temperature profiles and heat flux for various model interfaces with three different bonding-materials. (e) Comparison of the spectral heat flux of the three diamond-on-GaN models with different bonding-materials [187]. (f) Comparison of VDOS of AlN and diamond between planar interface and interface I-S3-H2 (nanopillars with size of  $2 \times 2$  nm² and height of 3 nm) [192]. (g) TBR values across  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond interfaces between different orientations of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [194]. O atom grouping diagrams (h) and thermal conductivity spectra (i) of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with different crystalline orientation. (j) Thermal conductivity spectra of diamonds with different crystalline orientation (*Copyright* © 2024, American Chemical Society) [175]. (k) Phonon cumulative correlation coefficients between GaN and Al<sub>x</sub>Ga<sub>1-x</sub>N on both sides of the interface. (l) Dependence of temperature distribution on compressive stress. (m) PPR on compressive strain [196]. (ICS: Interfacial coupling strength; B-M: Bonding-materials; CO: Crystal orientation; D&S: Doping and strain).